触发器的基本特征

在数字系统中,不仅要对二进信号进行算术运算和逻辑运算,还要把运算结果保存起来,这就需要具有记忆功能的逻辑单元电路。把这种能够存储一位二进制数码的基本单元电路统称为触发器。触发器有两个基本特征:

- 具有两个能自行保持稳定的基本状态,用来表示逻辑状态0和1,或者二进制数字0和1;

- 在不同信号的作用下,触发器可以被置为1状态或0状态;

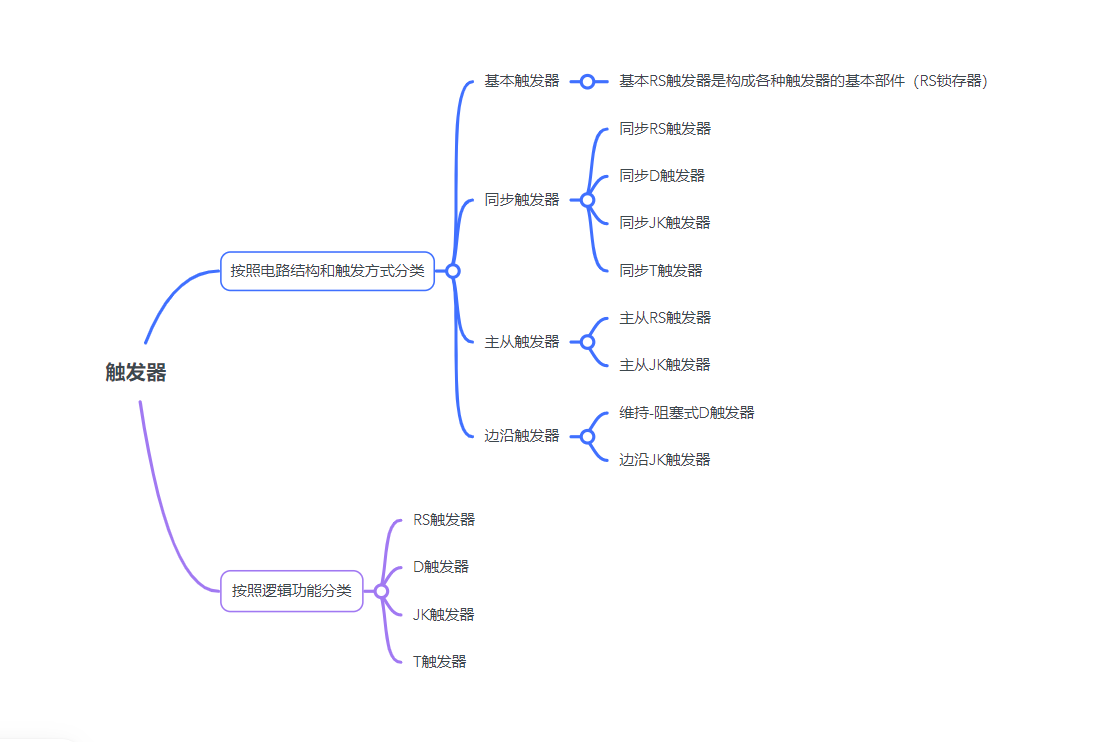

触发器种类

根据不同的维度,触发器将触发器分成不同的类别。

我们这里主要介绍我们即将使用的RS触发器和D触发器,更多关于触发器的内容,可以参考维基百科的介绍。

RS触发器

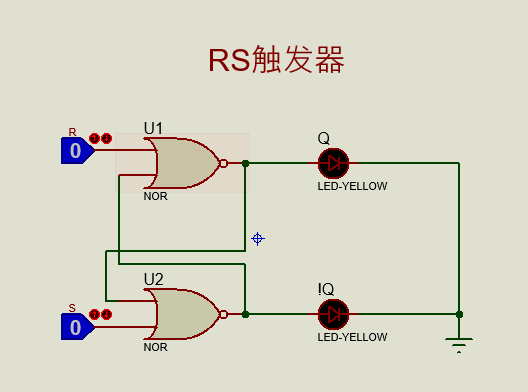

基本组成

真值表

| 输入 | 输出 | ||

|---|---|---|---|

| S | R | Q | Q的反相 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 0 | 保持 | 保持 |

| 1 | 1 | 禁止 | 禁止 |

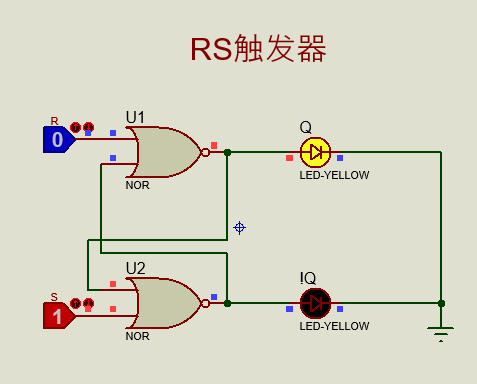

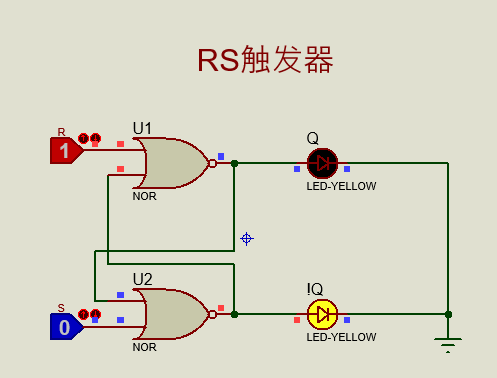

演示

- 置位:当置位位(S)为1,复位位(R)为0时,Q输出为1;

复位:当置位位(S)为0,复位位(R)为1时,Q输出为0;

保持:当从复位有效或者置位有效转为R和S都为0时,输出不改变。

结论

- RS触发器的特点在于,哪个输入端的最终状态为1。

- RS不能同时为1,非法;

- RS同时为0时,输出保持上一个输入的状态;

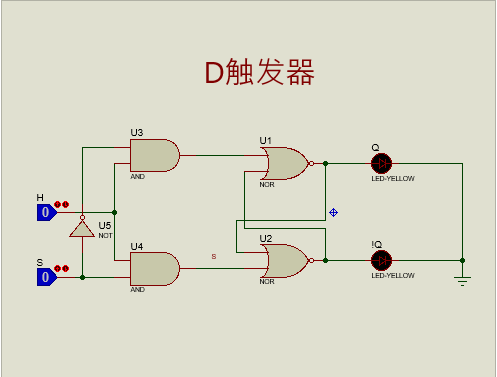

D触发器

我们在触发器分类的图中有提到,RS触发是其他触发器的基本组成单位,那么D触发器也不例外,它也是通过RS触发器和其他电路组合而来的,以解决新的问题。

针对RS触发器只能记住哪个输入端的最终状态为1,我们需要一个更聪明的电路,能够记住某个特定时间点上的信号是0还是1?

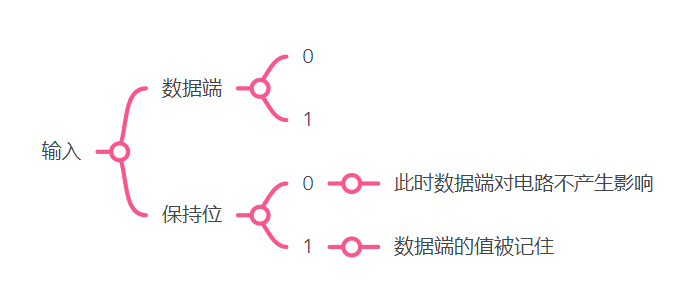

这个电路有两个输入,其中一个称为数据端、另一个成为保持位,它们满足以下功能:

我们将上述功能转换为真值表

| 输入 | 输出 | |

|---|---|---|

| 数据端 | 保持位 | Q |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

| 0 | 0 | Q |

| 1 | 0 | Q |

- 前两种情况下,保持位为1,输出Q与数据端输入相同;

- 后两种情况下,保持位为0,输出端Q和前一个状态保持一致;

RS触发器改进

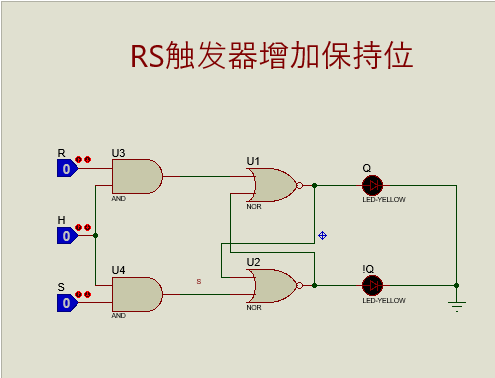

我们可以在RS触发器的基础上,加入两个与门来实现这个功能:电路如下:

它的特点是,当保持位为0时,置位位(S)和复位位(R)不会对电路的输出产生影响。

当保持位为1时,这套系统和RS触发器的功能一致。

但是,我们离目标还差一步,我们只想要两个输入,而不是三个。

我们回忆以下,RS触发器的功能表:

- 两个输入同时为1是非法,要尽量避免;

- 两个输入同时为0,是无意义的(不改变输出),

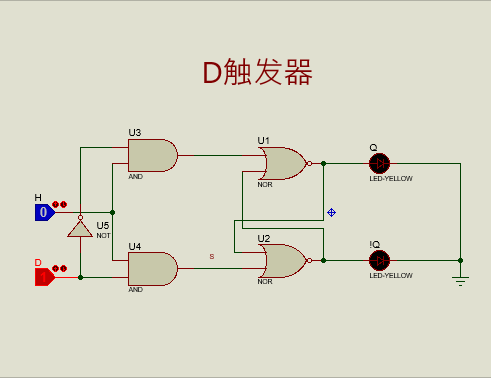

那么,我们只要将关注RS触发器的输入为0和1、1和0两种情况即可。我们把数据端看作是置位信号,把它取反看作是复位信号,可以画出如下的电路:

当保持位(H)为0时,数据端(S)对电路没有影响。

当保持位(H)为1时,可以记住数据端(S)的值。

D触发器

经过上边的改进,我们就得到了D触发器的结构。

D触发器的真值表如下:

| 输入 | 输出 | |

|---|---|---|

| 数据端 | 保持位 | Q |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

| X | 0 | Q |

结论

这个电路就是电平触发的D型锁存器,它表示电路锁住一位数据并保持它。在下一节,我们将用1位锁存器,组成8位锁存器来改进我们的加法器。